Half Adder (HA)

È il tipo di sommatore più elementare. L’Half Adder è un circuito che prende in input 2 bit e ne restituisce in output 2:

- La Somma .

- Il Resto .

La tabella di verità dell’Half Adder è così:

| 0 | 0 | ||

| 1 | 0 | ||

| 1 | 0 | ||

| 0 | 1 |

Nel pratico:

- Viene calcolata la somma tra gli input e , utilizzando la porta logica XOR.

- Viene ricavato il resto utilizzando l’AND.

Rappresentazione grafica del circuito logico:

Full Adder (FA)

Il Full Adder è un circuito logico che somma 3 bit in input e ne restituisce 2 in output.

- Input: , e <— La può essere usata anche come riporto dalla somma precedente (come nel caso dell’n-Bit Adder).

- Output:

- <— Somma finale.

- <— Riporto in uscita finale.

La tabella di verità del Full Adder è così:

| 0 | 0 | |||

| 1 | 0 | |||

| 1 | 0 | |||

| 0 | 1 | |||

| 1 | 0 | |||

| 0 | 1 | |||

| 0 | 1 | |||

| 1 | 1 |

Nel pratico:

- Un primo HA somma e , producendo una somma parziale e un riporto .

- Il secondo HA somma con , producendo la somma finale e un secondo riporto .

- Una porta logica OR finale, combina i due riporti e producendo il riporto in uscita finale .

Rappresentazione grafica del circuito logico:

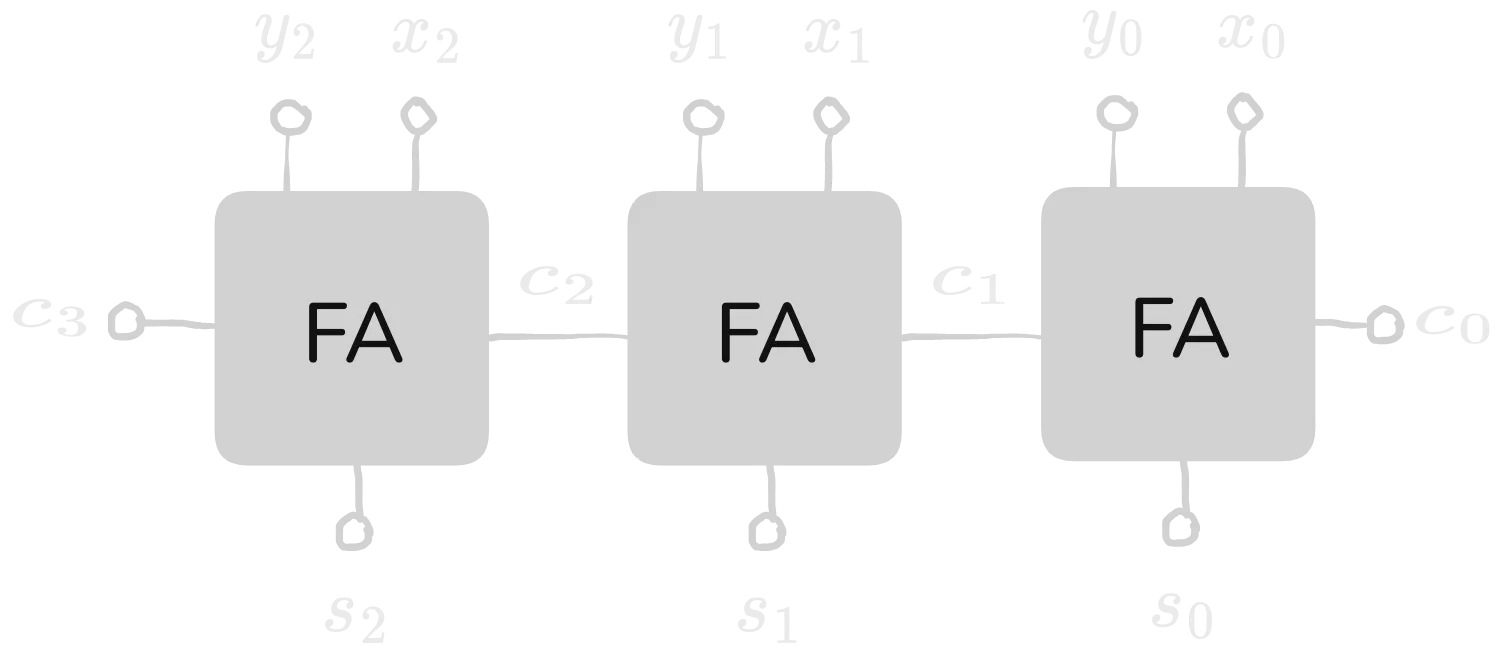

-Bit Adder (Ripple-Carry Adder)

L’-Bit Adder permette finalmente di riuscire a sommare anche numeri interi, in quanto somma due numeri di dimensione bit.

La struttura di questo sommatore è composta mettendo in cascata (in catena) una quantità di Full Adder pari alla dimensione in bit dei numeri da sommare.

Entrando nel pratico, ipotizziamo di dover sommare i seguenti due numeri:

Ipotizziamo adesso di costruire il nostro -Bit Adder concatenando Full Adder da destra verso sinistra:

- Il primo FA riceve in input , e , ossia il riporto dell’ultima somma, che non essendoci stata è un bit spento di default.

- Il primo FA restituisce in output la somma svolta tra e .

- Il primo FA restituisce anche il riporto in uscita finale , che viene collegato al del FA successivo (che in questo caso avrà in input , e il resto appena ottenuto).

- Questo processo si ripete, con il FA successivo verso sinistra e così via fino all’ultimo.

Rappresentazione grafica del circuito logico:

Continua con… Le Reti Logiche Combinatorie.